- easyDSP-F29H8XX(S)

基本晶片特色:

-

Three C29x 64-bit CPUs (CPU1, CPU2, CPU3) running at 200MHz

-

2x signal chain performance versus C28x with improved pipeline

-

Split lock and lockstep operating modes

-

-

C29x CPU architecture

-

Byte addressability

-

High-performance real-time control with low latency

-

High-performance DSP and general-purpose processing capabilities

-

VLIW CPU executes 1 to 8 instructions in parallel

Fully protected pipeline -

8/16/32/64-bit single-cycle memory operations, up to two 64-bit memory reads and one 64-bit memory write in a single-cycle

-

IEEE 32-bit and 64-bit floating operations

-

32-bit and 64-bit trigonometric operations

-

HW interrupt prioritization and nesting

-

11-cycle real-time interrupt response

-

Atomic operations with memory protection

-

Multi safe island code execution managed in hardware

-

-

Memory

-

4MB of CPU-mappable flash (ECC-protected) capable of supporting Firmware Over the Air (FOTA) with A/B swap and LFU

-

256KB of Data-only Flash (ECC-protected)

-

452KB of RAM (ECC-protected)

-

Dedicated 512KB Flash and 40KB RAM memories for HSM (ECC-protected)

-

Built in ECC logic for system-wide safety

-

-

Analog Subsystem

-

Five Analog-to-Digital Converters (ADCs)

-

Two 16-bit ADCs, 1.19MSPS each

-

Three 12-bit ADCs, 3.92MSPS each

-

Up to 80 single-ended or 16 differential inputs

-

40 redundant input channels for flexibility

-

Separate sample-and-hold (S/H) on each ADC for simultaneous sampling

-

Hardware post-processing of conversions

-

Hardware oversampling (up to 128x) and undersampling modes, with accumulation, averaging and outlier rejection

-

Programmable delay from SOC trigger to start of conversion

-

Ten ADC Safety Checkers for comparison of conversion results across multiple ADC modules

-

12 windowed comparators with 12-bit Digital-to-Analog Converter (DAC) references

-

Connection options for internal temperature sensor and ADC reference

-

Two 12-bit buffered DAC outputs

-

-

Control Peripherals

-

36 Pulse Width Modulator (PWM) channels, all with high-resolution capability (HRPWM)

-

Minimum Dead-Band Logic (MINDB)

-

Illegal Combo Logic (ICL) for standard and high resolution

-

Diode Emulation (DE) support

-

Multilevel shadowing on XCMP

-

Six Enhanced Capture (eCAP) modules

-

High-resolution Capture (HRCAP) available on two of the six eCAP modules

-

Two new monitor units for edge, pulse width and period that can be coupled with ePWM strobes and trip events

-

Increased 256 multiplexed capture inputs

New ADC SOC generation capability -

Six Enhanced Quadrature Encoder Pulse (eQEP) modules

-

16 Sigma-Delta Filter Module (SDFM) input channels, 2 independent filters per channel

Embedded Pattern Generator (EPG) -

Configurable Logic Block (CLB)

Six tiles -

Augments existing peripheral capability

-

Supports position manager solutions

-

-

Communications Peripherals

-

CAN FD:6 (CAN-FD)

-

SPI: 6 Sets

-

UART: 6 Sets

-

FSI, I2C, LIN, PMBUS, SENT

-

晶片方塊圖:

硬體模組特性:

-

包含F29H859TU8QPTSQ1處理器,可插拔式設計替換。

-

包含一組RS-232連接頭與一組排座

-

包含一組CAN連接頭與排座、包含終端電阻選擇

-

晶片腳位有拉出,包含GPIO、ADC和電源訊號

-

包含ePWM訊號輸出,最多擁有32個通道

-

ADC 通道輸入並有電壓保護裝置穩壓3.3V,不必外加齊納二極體 ,本身ADC共有26個輸入通道。

-

ADC 通道輸入並包含Anti-aliasing filter (noise filter)功能,可做基本低通濾波電路

-

透過CCSv20+軟體進行程式除錯,支援程式燒錄等功能

-

兩組可控制的LED顯示燈

-

支援隔離式ISO-JTAG轉接介面

-

支援開機模式設定

-

使用5V 電源

-

可提供最高至1A電流輸出給周邊電路

發展工具 - 開發環境與軟體:

| 開發環境 | 型號 | 說明 |

|

|

最新一代XDS11x USB介面模擬器 ,添加隔離式介面,可支援CCS6.x以上版本。(提供比上一代更高五倍的傳輸速度)New!。 | |

|

支援串列訊號TTL轉USB介面,採用隔離式介面 New! | |

|

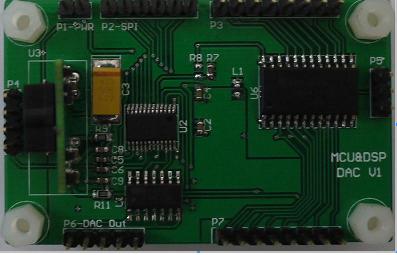

提供單極性電壓輸出控制模組,支援標準SPI介面,相容於C2000/MSP430系列所有晶片 | |

|

|

提供正負雙極性電壓輸出控制模組,支援標準SPI介面,相容於C2000/MSP430系列所有晶片 | |

|

|

Micro SD儲存裝置(easyDSP-SD Card) |

採用SPI介面資料傳輸,可以相容各式DSP與MCU處理晶片 |

|

雙核心浮點DSP運算控制多功能資料擷取卡,提供豐富的教學程式與範例 | |

|

結合TI DSP處理器的CAN匯流排開發套件 | |

|

4通道降壓轉會模組 | 類比電壓準位轉換模組 |

|

4通道升壓轉換模組 | 類比電壓準位轉換模組 |